[Chip Hall of Fame] ชิป 4Kb DRAM ตัวแรกที่จะปฏิวัติโครงสร้าง DRAM ไปตลอดกาล : Mostek MK4096

RAM ( Random Access Memory ) คือหนึ่งในส่วนสำคัญของระบบคอมพิวเตอร์ ซึ่ง RAM นั้นมีอยู่ 2 แบบคือ SRAM และ DRAM โดย SRAM เป็น RAM ที่เมื่อมีการเขียนข้อมูลแล้ว ข้อมูลจะยังคงอยู่ตรงนั้นตราบเท่าที่ยังคงมีการจ่ายไฟเลี้ยงให้มัน ส่วน DRAM เป็น RAM ที่จะต้องคอยมาเขียนข้อมูลซ้ำอยู่สม่ำเสมอ มิฉะนั้นข้อมูลอาจจะมีการสูญหาย แต่เรื่องนี้ไม่ใช่ปัญหาใหญ่ สำหรับการใช้งาน DRAM อย่างแน่นอน เพราะมันถูกออกแบบมาเพื่อเป็นที่พักข้อมูลชั่วคราวระหว่างรอประมวลผล เมื่อประมวลผลเสร็จสิ้นก็จะมีการนำข้อมูลใหม่มาวางที่เดิมอยู่แล้ว และโครงสร้างของ DRAM เองที่มีความเรียบง่าย ใช้พื้นที่น้อย สามารถบรรจุหน่วยความจำได้มากบนชิปตัวเล็กๆ ทำให้ DRAM นั้นมีการใช้งานอย่างแพร่หลายมาก

ชิป DRAM ตัวแรกนั้นออกแบบโดย บริษัท Intel แต่ชิป MK4096 ขนาด 4 Kb ของ Mostek ที่เรามานำเสนอในวันนี้ เป็นชิปสำคัญที่จะเปลี่ยนโครงสร้างของชิป DRAM ไปตลอดกาล แต่ก่อนอื่นคงต้องมาเริ่มที่โครงสร้างของชิป DRAM ก่อนการมาถึงของ MK4096 กันก่อน เพื่อให้เข้าใจในข้อจำกัด และความสำคัญของสิ่งที่มีเพิ่มขึ้นมาใน MK4096 ตัวนี้

ในช่วงก่อนหน้านั้น DRAM ที่มีให้ใช้กันมีขนาดจำกัด โดยทั่วไปจะมีประมาณ 1Kb ที่มาพร้อมกับ Package IC ขนาด 16 ขา

ซึ่งจะประกอบไปด้วยขาไฟเลี้ยง 2 ขา คือ VCC และ GND

ขาควบคุมชิป 2 ขา คือ CE ( Chip Enable ) ที่ใช้เลือกชิปที่จะติดต่อ และขา R/W ( Read/Write ) ที่ใช้สำหรับเลือกว่าจะเขียนข้อมูลหรืออ่านข้อมูล

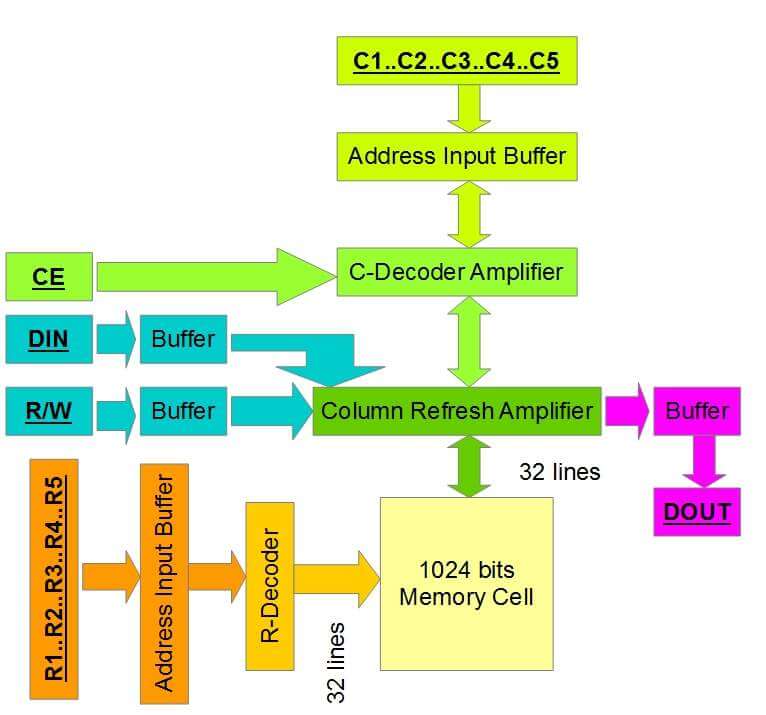

ขาสำหรับระบุตำแหน่ง ( Address ) อีก 10 ขา โดยแบ่งเป็นเลือกตำแหน่งบนหลัก ( Column ) 5 ขา และตำแหน่งบนแถว ( Row ) อีก 5 ขา โดยสัญญาณจากทั้ง 5 ขาของทั้งหลัก และแถวนั้น จะถูกนำไปขยายออกเป็น 32 ขา โดยอ้างอิงตามค่าของเลขฐานสอง เพื่อเข้าถึง Memory Cell แต่ละแหน่ง ดังนั้น เมื่อสัญญาณของแถว 32 แถว และหลัก 32 หลัก จะทำให้อ้างอิงตำแหน่งของ Memory Cell ได้ทั้งหมด 1024 ตำแหน่ง ( 32×32 = 1024 )

และมีขาข้อมูล 2 ขา คือขารับข้อมูลเข้าที่ใช้เวลาต้องการเขียนข้อมูล และขาส่งข้อมูลออกที่ใช้เมื่อต้องการอ่านข้อมูล

โครงสร้าง DRAm ขนาด 1 Kb

โครงสร้างชิปแบบนี้มีข้อจำกัดคือ ยิ่งหน่วยความจำมีขนาดใหญ่มากขึ้นเท่าไหร่ จำนวนขาเพื่อใช้ระบุตำแหน่งจะต้องมีมากขึ้นอย่างมาก เช่น ชิปในตัวอย่างมีขา 16 ขา มีขาอ้างอิงตำแหน่ง ( Address ) ทั้งหมด 10 ขา มีหน่วยความจำขนาด 1 Kb แต่หากใช้วิธีเดียวกันบนหน่วยความจำขนาด 4 Kb มีความจำเป็นที่จะต้องเพิ่มขาระบุตำแหน่งอีก 2 ขา เพื่อให้สามารถอ้างอิงบนหลัก 64 หลัก และแถว 64 แถวได้ ( 64×64 = 4096 ) แต่เมื่อหน่วยความจำมีขนาดเพิ่มเป็น 64 Kb จำนวนของขาที่จะต้องใช้ในการระบุตำแหน่งจะต้องเพิ่มกลายเป็น 16 ขา ( หลัก 8 ขา และแถว 8 ขา ) เพิ่มขึ้นจาก DRAM 1 Kb ถึง 6 ขา และเมื่อรวมกับขาสัญญาณอื่นๆ จะทำให้ชิปตัวนี้มีขามากถึง 32 ขาเลยทีเดียว ทั้งหมดนั้นคือต้นทุนที่จะขยับตามจำนวนขาและขนาดของ Package IC

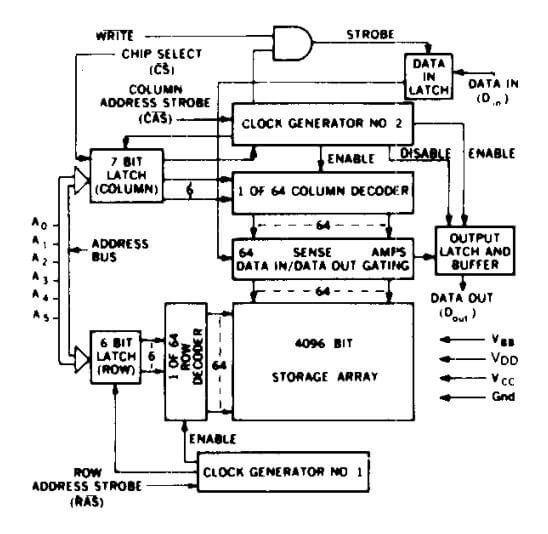

วิธีที่ Mostek ใช้คือ พวกเขาเลือกที่จะใช้วิธีอ่านสัญญาณสลับกัน บนขาระบุตำแหน่งเดียวกัน – Multiplexing ดีไซน์ของพวกเขาจำเป็นต้องเพิ่มขาสัญญาณเพื่อควบคุมขึ้นมาอีก 2 ขา นั่นคือขา CAS และ RAS เพื่อแยกแยะระหว่างชุดสัญญาณของหลัก ( Column ) และแถว ( Row ) ซึ่งชิปจะนำสัญญาณนั้นไปกับไว้ในวงจร Latch Register เพื่อคงสถานะของสัญญาณไว้ ทำให้สัญญาณยังคงเดิมอยู่ แม้ว่าสัญญาณใหม่จะเข้ามา เพื่อนำไปใช้กับอีกด้านหนึ่งก็ตาม

เช่น เมื่อเราต้องการเข้าถึงตำแหน่งที่ 2048 เราต้องใส่สัญญาณระบุตำแหน่งที่ 32 ของหลัก และ 64 ของแถว เราก็จะใส่ค่า 32 (b0100000) ลงในขาระบุตำแหน่ง และให้สัญญาณ CAS เพื่อให้ชิปนำค่า 32 นี้ไปเก็บในวงจร Latch ของหลัก จากนั้นรีเซ็ตสัญญาณ CAS แล้วเราจึงใส่ค่า 64 ( b1000000 ) ลงในขาระบุตำแหน่ง และให้สัญญาณ RAS เพื่อให้ชิปนำค่า 64 นี้ไปเก็บในวงจร Latch ของแถวอีกที เมื่อมีทั้งสัญญาณหลัก ที่มีค่า 32 และสัญญาณแถวที่มีค่า 64 ทำให้เราสามารถเข้าถึงหน่วยความจำที่ 2048 ได้ โดยใช้ขาระบุตำแหน่งชุดเดียวกัน

โครงสร้าง DRAM – MK4096K

นั่นแปลว่าที่หน่วยความจำขนาด 64 Kb มีความเป็นไปได้ที่มันจะอยู่ใน Package IC ขนาด 16 ขา เหมือนกับหน่วยความจำขนาด 1 Kb และนั่นคือต้นทุนที่ลดลงมหาศาล และการเปิดกว้างในการเข้าถึงชิปหน่วยความจำที่มีราคาถูกลงในขณะที่มีความจุมากขึ้น ซึ่งในปัจจุบันเราก็ยังคงระบุตำแหน่งหน่วยความจำผ่านขาชุดเดียวกันอยู่ครับ

อ้างอิง

http://spectrum.ieee.org/semiconductors/memory/chip-hall-of-fame-mostek-mk4096-4kilobit-dram

MK4096 Datasheet

http://www.datasheetframe.com/PDF/MK4096N-6-PDF/660013

Basic SRAM-DRAM

http://archive.arstechnica.com/paedia/r/ram_guide/ram_guide.part1-4.html

DRAM – 1 Kb – 4 Kb

http://www.primrosebank.net/computers/mtx/components/memory/dram/dram.htm

**บทความนี้เป็นส่วนหนึ่งของบทความชุด Chip Hall of Fame ซึ่งแปลมากจาก IEEE Spectrum คุณสามารถดูตอนอื่นๆได้ที่หน้ารวมบทความ

[Chip Hall of Fame] ชิปวงจรรวมในตำนาน #เกริ่นนำ หรือ แท็ก Chip Hall of Fame